Giới thiệu

- PIC18F4550 có mô-đun CCP sẵn có có chế độ Chụp, So sánh và chế độ PWM cho các ứng dụng khác nhau.

- Chế độ CCP trong So sánh được sử dụng để tạo ra dạng sóng của chu kỳ nhiệm vụ khác nhau như PWM và cũng được sử dụng để kích hoạt sự kiện khi thời gian được xác định trước hết hạn.

- Ngoài ra nó được sử dụng để tạo ra thời gian trễ cụ thể.

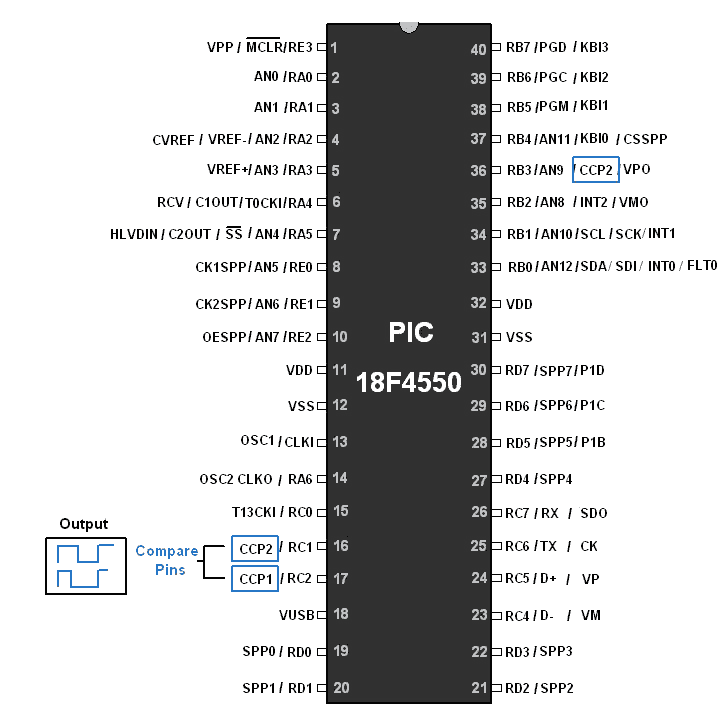

- PIC18F4550 có 2 mô-đun CCP được xây dựng sẵn, ví dụ CCP1 và CCP2.

- Đầu ra (ví dụ tạo dạng sóng) của CCP2 và CCP1 trong chế độ so sánh được tạo ra trên hai chân tức là RC1 và RC2 tương ứng.

Chân mô-đun của CCP

PIC18F4550 So sánh chế độ Ghim

Đăng ký CCPR1

Mô-đun CCP có đăng ký 16 bit CCPR1 [CCPR1H (8-bit): CCPR1L (8-bit)] được đưa ra dưới đây, trong đó số được tải để so sánh.

Đăng ký CCPR1

Chế độ so sánh của mô-đun CCP được chọn bằng cách sử dụng các bit trong Đăng ký CCP1CON.

Chỉ có thể sử dụng Timer1 và Timer3 cho chế độ So sánh trong PIC18F4550.

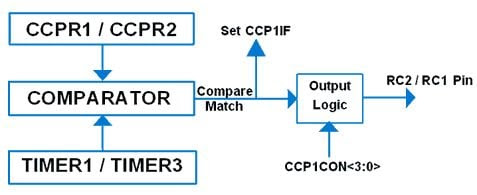

Hoạt động của chế độ So sánh

Hoạt động của chế độ So sánh

Trong chế độ so sánh, giá trị đăng ký CCPR1 16 bit được so sánh liên tục so với giá trị cặp đăng ký TMR1 hoặc TMR3 được hiển thị trong hình bên dưới.

Khi khớp xảy ra giữa giá trị đăng ký CCPR1 và giá trị Timer, cờ ngắt CCP1IF được tạo và một trong các hành động sau có thể xảy ra trên pin RC2 liên quan:

- Chuyển đổi đầu ra trên chân RC2.

- RC2 pin ổ đĩa đến mức cao.

- RC2 pin ổ đĩa đến mức thấp.

- Tạo phần mềm gián đoạn

- Tạo sự kiện kích hoạt đặc biệt.

Bây giờ logic đầu ra sẽ tạo ra khi so sánh so sánh xảy ra phụ thuộc vào đăng ký CCP1CON.

Đăng ký CCP1CON: Đăng ký kiểm soát CCP1

Đăng ký CCP1CON

DC1B1: DC1B0 :

Được sử dụng cho chế độ PWM.

CCP1M3: CCP1M0 : bit lựa chọn chế độ mô-đun CCP1

Các bit này quyết định hành động nào sẽ thực hiện đối sánh so sánh.

0010 = Chuyển đổi đầu ra trên khớp

1000 = Initialize pin CCP1 thấp, trên so sánh phù hợp với pin này được thiết lập

cao.

1001 = Khởi tạo pin CCP1 cao, trên so sánh khớp với pin này được đặt

quá thấp.

1010 = Khi so khớp trùng khớp tạo ra phần mềm gián đoạn.

1011 = Khi sự kiện đặc biệt kích hoạt đối sánh so khớp, hãy đặt lại hẹn giờ, bắt đầu

ADC chuyển đổi.

Vì vậy, Cấu hình chế độ so sánh theo ứng dụng bằng cách sử dụng Đăng ký CCP1CON.

Các kết hợp khác được sử dụng cho chế độ Chụp và chế độ PWM.

Ngắt trên trận đấu

Cũng nên nhớ rằng sau mỗi trận đấu so sánh giữa cờ ngắt CCPR1 và Timer1 / Timer3 CCP1IF được thiết lập.

Lá cờ này được đặt tại PIR1 <bit2> Register.

Cũng lưu ý rằng thanh ghi T3CON được sử dụng để chọn Timer1 hoặc Timer3 cho chế độ so sánh.

T3CON Đăng ký : Timer3 Control Register

Đăng ký T3CON

T3CCP2: T3CCP1 : Được sử dụng để chọn Chế độ hẹn giờ cho chế độ So sánh.

00 = Timer1 cho cả hai mô-đun CCP

01 = Timer1 cho mô-đun CCP1

Timer3 cho mô-đun CCP2

1x = Timer3 cho cả hai mô-đun CCP

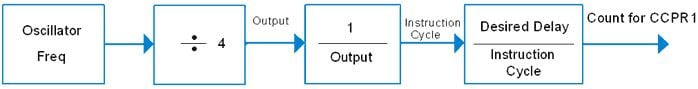

Phép tính

Bây giờ làm thế nào để tính toán Count cho CCPR1?

Hình dưới đây minh họa các bước tính toán cho độ trễ mong muốn được tải vào thanh ghi CCPR1.

Các bước tính toán cho số CCPR1

Các bước lập trình

- Đặt chốt CCP1 làm đầu ra.

- Cấu hình T3CON Đăng ký Timer1 hoặc Timer 3

- Nếu sử dụng Timer1 thì hãy định cấu hình Đăng ký T1CON.

- Định cấu hình Đăng ký CCP1CON cho chế độ so sánh.

- Tải số lượng mong muốn trong CCPR1 (CCPR1H: CCPR1L) Đăng ký.

- Đồng thời khởi tạo giá trị Đăng ký TMR1 hoặc TMR3.

- Bắt đầu hẹn giờ

- Đợi cờ ngắt CCP1IF (PIR1 <2>) để cài đặt.

- Sau đó, Clear Timer Register (TMR1 hoặc TMR3).

- Chuyển sang bước 3.

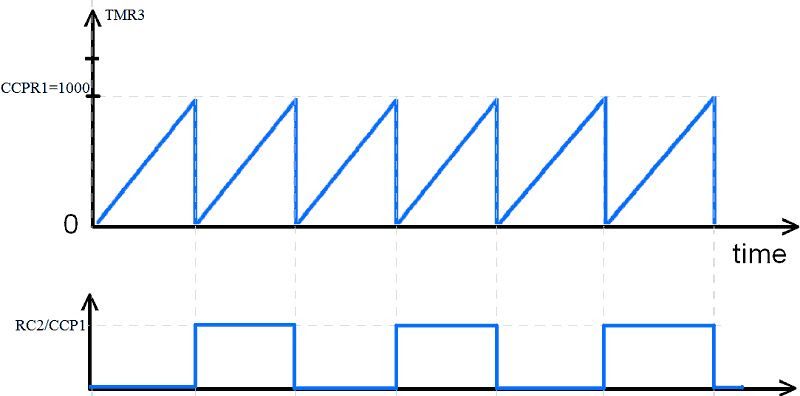

Ứng dụng 1

Ở đây chúng ta hãy tạo ra một làn sóng vuông 1 KHz có chu kỳ nhiệm vụ 50%.

Cho 50% chu kỳ nhiệm vụ

Giả sử tần số dao động = 8MHz

Thời gian của dạng sóng = 1ms (1 KHz đã cho)

Chu trình Chỉ thị = 1 / (FOSC / 4) = 1 / (8MHz / 4) = 0.5

Điều đó có nghĩa là Timer sẽ tăng số lượng liên tục sau mỗi lần trì hoãn 0.5us.

Ở đây tôi sử dụng Timer3 đăng ký.

Bây giờ tính toán số CCPR1.

Đối với chu kỳ nhiệm vụ 50% - ON time = OFF time = 0.5ms

0,5ms / 0,5us = 1000 tức là 0x03E8

CCPR1 = 0x03E8

#include "osc.h"

#include <p18f4550.h>

void main()

{

OSCCON=0x72; /* Configure internal clock at 8MHz */

TRISCbits.TRISC2=0; /* Configure RC2 pin as output */

CCP1CON=0x02; /* Module is configured for compare mode and is set up so that upon a compare match of CCPR1 and TMR3, RC2 is driven low*/

PIR1bits.CCP1IF=0; /* Clear interrupt flag*/

TMR3=0; /* Clear Timer3 Register*/

T3CON=0xC0; /* Timer3 used for compare mode with TMR3 register in 16-bit format*/

CCPR1=1000; /* Load a count for generating 1khz*/

T3CONbits.TMR3ON=1; /* Turn On Timer3*/

while (1)

{

/* Wait for CCP Interrupt flag to set, it is set on compare match between CCPR1 and TMR3*/

while(PIR1bits.CCP1IF==0);

PIR1bits.CCP1IF=0;/* Clear interrupt flag */

TMR3=0;

}

}

Đầu ra

Ứng dụng 2

Bây giờ tạo ra một dạng sóng 1KHz khác với chu kỳ nhiệm vụ 40%.

Đối với chu kỳ nhiệm vụ 40% ,

ON time = 0.4ms, OFF time = 0.6ms

0,4ms / 0,5us = 800 tức là 0x0320

0,6ms / 0,5us = 1200 tức là 0x04B0

Tải các giá trị này vào CCPR1

#include "osc.h"

#include <p18f4550.h>

void main()

{

OSCCON=0x72; /* Configure internal clock at 8MHz */

TRISCbits.TRISC2=0; /* Configure RC2 pin as output. */

CCP1CON=9; /* Module is configured for compare mode and is set up so that upon a compare match of CCPR1 and TMR3, RC2 is driven high*/

PIR1bits.CCP1IF=0;

TMR3=0;

T3CON=0xC0; /* Timer3 used for capture mode with TMR3 register in 16-bit format*/

CCPR1=0x320; /* Load a count for generating 0.4ms*/

T3CONbits.TMR3ON=1; /* Turn On Timer3*/

while(1)

{

/* Wait for CCP Interrupt flag to set, it is set on compare match between CCPR1 and TMR3*/

while(PIR1bits.CCP1IF==0);

PIR1bits.CCP1IF=0; /* Clear interrupt flag*/

TMR3=0; /* Clear Timer3 Register*/

CCP1CON=8; /* CCP1 module is configured for compare mode and is set up so that upon a compare match of CCPR1 and TMR3, RC2 is driven low*/

CCPR1=0x04B0; /* Load count for generating 0.6ms */

while(PIR1bits.CCP1IF==0);

PIR1bits.CCP1IF=0;

TMR3=0; /* Clear Timer3 Register*/

CCP1CON=9;

CCPR1=0x0320; /* Load count for generating 0.4ms */

}

}

Đầu ra

Không có nhận xét nào:

Đăng nhận xét